オピニオン

半導体後工程における基板材料の進化

2025年05月21日 金子大亮

本稿の概要

これまで半導体の処理能力の向上と消費電力の低減は前工程における微細化によって実現されてきた。しかし、近年では前工程における微細化の限界に伴い、半導体の進化の主導権が前工程から、ガラスコア基板やRDLインターポーザーなどの後工程の三次元実装技術に移り変わり始めている。最新の三次元実装技術の実現には新たな装置や材料を顧客ニーズと高度にすり合わせ、複雑なニーズに対応することが成功のカギとなる。そのため、精密加工や機能性材料における条件だしや調整のノウハウを有し、すり合わせを得意としている日本の半導体関連の装置・材料メーカーにとってビジネスチャンスとなる可能性が高い。日本の装置・材料メーカーは、業界の垣根を越えて、これまで個社で培ってきた材料・装置における技術を、三次元実装技術に活用することを目指すべきである。

1. 半導体の性能向上の必要性

昨今の半導体において、処理能力の向上と消費電力の低減は至上命題である。高グラフィックな動画視聴やゲームの需要の高まりが半導体の性能向上が必要な理由の一つである。そして、生成AIの開発および利用のための主にデータセンターでの大規模な計算需要が半導体の性能向上が必要な最大の理由である。GPU(Graphics Processing Unit、画像処理装置)等のデータセンターで用いられる半導体では、大規模な計算を早く処理するための能力はもちろんのこと、電力消費量と熱の発生が大きな課題となっており、消費電力の低減も強く求められている。

2. 半導体性能向上方法の移り変わり「前工程から後工程へ」

これまで半導体の処理能力向上と消費電力低減は「半導体集積回路におけるトランジスタの集積密度は2年ごとに2倍になる」というムーアの法則にしたがった半導体前工程における微細化技術によって達成されてきた。現在も台湾セミコンダクター・マニュファクチャリング・カンパニー (TSMC) 、サムスン電子、インテルといった半導体チップ製造事業者が微細化技術を競い合っている。微細化においては上記3社および露光装置メーカーASML等が中心となっている。しかし、これまでムーアの法則に従ってきた前工程における微細化による集積密度の向上は限界が近づいている。

現在の最先端半導体では微細化のために波長の短いEUV(Extreme Ultraviolet、極端紫外線)光源が利用されている。EUV露光装置における開口数を高めることによってさらなる微細化が進められているが、開口数の向上にはいくつかの大きな課題がある。まず、EUV露光には表面粗さ50pm(ピコメートル、ピコは10-12)以上の精度のレンズ(EUVは反射光学系であるため一般的な透過レンズとは異なりミラーレンズである)が必要であり、高開口数を実現するにはレンズを巨大化する必要がある。巨大なレンズを超高精度に研磨することは大変難しく、大きな課題となっている。また、EUV露光ではスズ(Sn)の液滴に炭酸ガスレーザーを当てることでEUV光を発生させており、高開口数にするにはEUV高を高エネルギーにする必要がある。炭酸ガスレーザーからEUV光への変換とウェーハ照射までの経路での損失から、高エネルギーEUV光のために多くの電力を必要とすることが大きな課題となっている。半導体業界向けの情報プラットフォームであるTech InsightsではEUV露光機を備えるファブの合計電力消費量は、2030年までに年間 5万4,000GWhを超えると予測している(※1)。これはシンガポールやギリシャなど多くの国が年間に消費する電力量を上回っており、大きな課題である(※2)。上記のように、前工程におけるさらなる微細化には大きな課題があり、前工程による集積密度の向上は限界が近づいている。

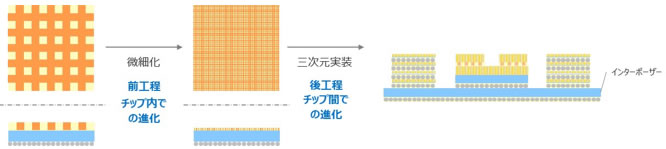

前工程における微細化の限界に伴い、三次元実装等の後工程による半導体の性能向上が進められている。前工程ではチップ内の微細化によって信号伝送経路を短縮して処理速度の向上と消費電力低減を実現していたのに対し、後工程ではチップの実装間隔を狭めることやチップ間の配線を緻密にすることによって信号伝送経路を短縮して処理速度の向上と消費電力低減を実現している。チップの間隔短縮化、チップ間配線緻密化のために同一パッケージ内に複数チップを実装するSiP(System in Package、システムインパッケージ)やインターポーザー(中間基板)に複数チップを実装する2.5Dパッケージが用いられている。

図1 前工程と後工程による半導体性能向上方法(模式図)

3. 三次元実装における新たな技術

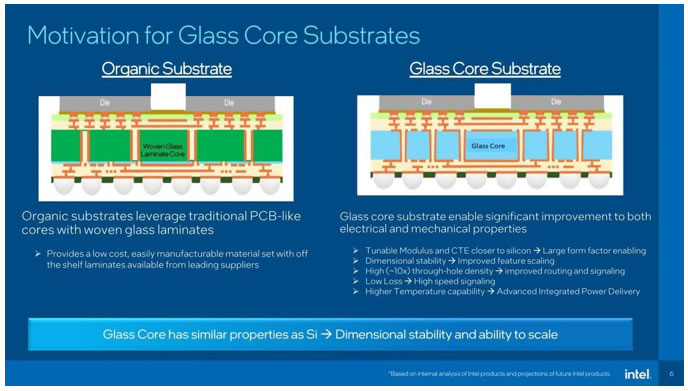

(1) ガラスコア基板

現在、半導体のパッケージ基板には機械的特性および科学的安定性の高さとコストの低さからガラスエポキシ樹脂が用いられている。これに対し、インテルが2023年にEMIB(Embedded Multi-Die Interconnect Bridge、エンベデッド・マルチダイ・統合ブリッジ)以降の世代の先端技術としてガラスコア基板を発表するなどパッケージ基板にガラスを用いたガラスコア基板が登場している(※3)。ガラスコア基板の導入の主な動機は、基板の反りの低減によってパッケージの大型化が可能である点と、優れた誘電特性によって配線間隔の短縮、微細化が可能な点の2点である。

図2 インテルのガラスコア基板紹介資料抜粋(※3)

A. 大型基板における基板反りの低減

電力効率と高速処理を求める昨今の半導体では同一パッケージ内への複数チップの実装が盛んに行われ、パッケージ基板は年々大きくなっている。パッケージの大型化における最大の課題は、チップのシリコンと基板のガラスエポキシ樹脂の熱膨張係数の差による実装工程後の反りである。反りそのものがマザーボードへの実装の際に問題になるうえ、反りによってチップ接合部にクラックが入ってしまうことも問題である。ガラスエポキシ樹脂ではなくガラスであれば、熱膨張係数がシリコンに近く、ヤング率が大きいために反りが発生しにくい。以上がガラスコア基板を導入する一つ目の動機である。

B. 微細配線の形成

ガラスはガラスエポキシ樹脂に比べて誘電率等の電気的特性が優れているため、微細な配線間隔での利用が可能である。また、ガラスはガラスエポキシ樹脂に比べて平滑性が高く、剛性が優れているため、配線のための微細なビアを開けることが可能である。したがって、ガラスコア基板はガラスエポキシ樹脂より微細配線の形成が行いやすい。以上がガラスコア基板を導入する二つ目の動機である。

以上の利点を生かして、ガラスコア基板においてインターポーザーに形成するレベルの微細配線の形成が可能であれば、インターポーザーを用いずにチップレットやHBM(High Bandwidth Memory、広帯域メモリ)の実装が可能になることで、コスト低減におよびパッケージ基板のさらなる大型化によって高効率なプロセッサーモジュールを作ることが可能になる。一般に、データセンターではAI向けやHPC(High Performance Computing、高性能計算)向け半導体として電力効率化および高速化のニーズがあり、大型パッケージ基板を必要としている。そのため、ガラスコア基板は、主にデータセンターで利用される見込みである。

(2) RDLインターポーザー

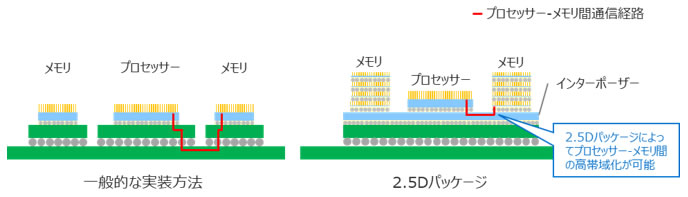

最先端のGPUとメモリの実装においては、プロセッサーとメモリとの間の通信経路短縮のための、インターポーザーを利用した実装である2.5Dパッケージが盛んに利用されている。TSMCの「CoWoS」がその代表例であり、シリコン製のインターポーザーが用いられている。

図3 2.5Dパッケージによるプロセッサーとメモリの間の通信経路短縮(模式図)

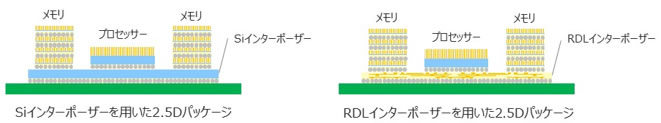

シリコン製のインターポーザーは前工程プロセスを用いて非常に薄く加工しなければならないうえ、高平坦(低GBIR(Global Backside Ideal Range、裏面基準グローバル平坦度)、低TTV(Total Thickness Variation、全厚さばらつき))かつ高平滑(低表面粗さ)に加工する必要があり、高コストであることと、大型化が困難であるという課題がある。これに対し、インターポーザーとしてリジッドな基板を用いないFOWLP(Fan Out Wafer Level Package、ファン・アウト型ウェーハレベルパッケージ)、FOPLP(Fan Out Panel Level Package、ファン・アウト型パネルレベルパッケージ)技術を用いたRDL(Redistribution Layer、再配線層)インターポーザーが注目されており、TSMCやサムスン電子で開発が行われている。

図4 シリコンインターポーザーとRDLインターポーザー

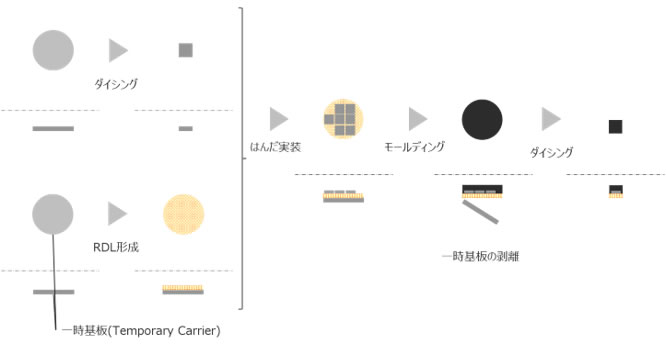

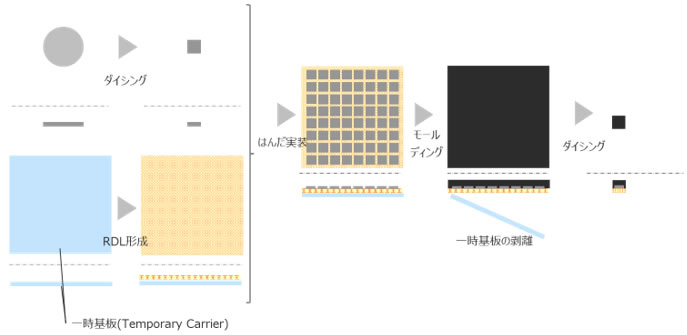

FOWLPはもともと単一チップの実装技術として最先端ロジックで用いられてきた。FOWLPでは一時基板(Temporary carrier(別名:キャリア))にRDLを形成し、チップを実装した後に一時基板を剥離するプロセスが行われる。FOWLPでは一時基板にシリコンウェーハが用いられる。シリコンウェーハは一般に用いられている300mmウェーハの他、一部では450mmウェーハ等も開発されているが、大きさに限界があるうえ、丸型であるため端部に材料の無駄が生じる。

図5 FOWLP工程模式図

そこで角型の基板を一時基板として用いることで大型化および無駄な部分を省くことによるパッケージの取れ効率を上昇させたFOPLPが開発され、サムスン電子のGalaxy Watch向けのAP(Application processer、アプリケーションプロセッサー)(※4)やPMIC(Power Management IC、電源管理IC)等で用いられている。

図6 FOPLP工程模式図

4. 新技術における新装置・新材料の動向

(1) ガラスコア基板

大日本印刷が2023年に次世代半導体パッケージ向け「TGV(Through Glass Via、ガラス貫通電極)ガラスコア基板」の開発を(※5)、日本電気硝子が2024年にCO₂レーザーで穴あけ加工ができる新型ガラスコア基板の開発に着手したと発表している(※6)。ガラスコア基板では貫通穴の内壁に銅などの導電材料をむらなく成膜する必要がある。大日本印刷では、印刷プロセスで培い、半導体用フォトマスクやMEMS(Micro Electro Mechanical Systems、微小電子機械システム)製造によって磨いてきた微細加工技術を生かして高品質なガラスコア基板を実現する。日本電気硝子ではディスプレー向けガラスで培ってきた高品質板ガラス製造技術を生かして高品質なガラスコア基板を実現する。

ガラス基板の熱膨張率の最適化やガラスへの微細な穴あけ技術の開発など、ガラスコア基板の実用化には多くの課題があり、ガラスコア基板の実用に向けて材料や装置の開発が求められている。

(2) RDLインターポーザー

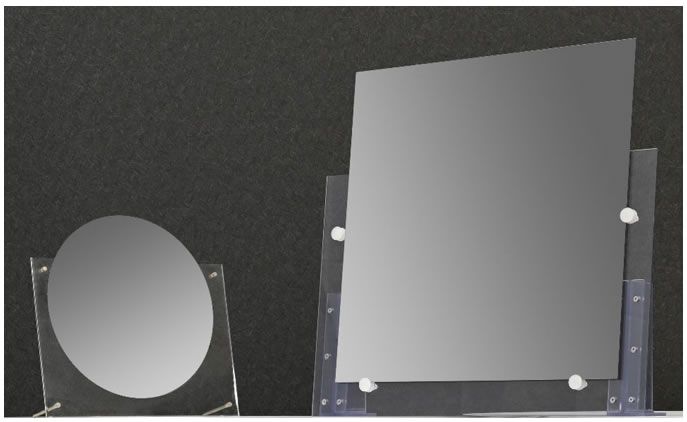

RDLインターポーザーへの活用によってFOPLPは重要な最先端半導体実装技術となっている。角型の一時基板にはガラスが用いられており、ここでもガラスコア基板と同様に、ガラスの剛性および平坦性が必要とされている。FOPLPの製造事業者としては既に生産を行っているサムスン電子の他、TSMC、Rapidus等のファウンドリが参入を表明している。さらに、これまで半導体に関わってこなかったジャパンディスプレイ(JDI)、イノラックス等の液晶ディスプレーパネルメーカーも大型パネル製造技術を生かして参入を表明している(※7)(※8)。

角型の基板を採用するには従来の丸型のウェーハプロセスから角型の基板用のプロセスを構築する必要があり、露光装置や検査装置についても角型基板専用の装置が必要となる。キヤノンは解像力1.0μmで515×510mmまでの大型角型基板に対応するi線ステッパー「FPA-8000iW」を提供しており(※9)、東レエンジニアリングは角型に対応可能な大型ガラス基板向け光学式外観検査装置の販売を2025年3月から開始している。(※10)。いずれも日本企業がこれまで培ってきた精密加工技術や精密検査技術を生かした製品となっている。

現在は一時基板としてガラスが用いられており、ディスプレー用にガラスを製造してきたAGC(※11)や日本電気硝子(※12)のガラスが利用されている。当面はガラスが用いられると考えられるが、ガラスは熱伝導率が低いために偏熱によって露光工程において基板面内でばらつきが発生する等の課題が存在する。日本電気硝子はガラス粉末とセラミックス粉末の複合材を用いた「GCコア」の開発を発表しており(※13)、三菱マテリアルは600mm角の「角型シリコン基板」の開発を発表している(※14)。こちらも日本企業が培ってきた、最適特性のための素材配合ノウハウや精密研磨等の材料加工技術を強みとして生かした製品となっている。

FOPLPによるRDLインターポーザーの実現および高度化のためには多くの課題があり、これまでの半導体業界にはない材料や装置の開発が求められている。

図7 三菱マテリアルが開発した角型シリコン基板(510mm×515mm×0.8mm)とサイズ比較用の300mmウェーハ(※14)

5. おわりに

半導体の進化の主導権が前工程における微細化から後工程における三次元実装に移り変わろうとしていることで、後工程において装置、材料の新規開発が求められており、さまざまな企業においてビジネスチャンスとなっている。半導体に用いられなかった材料が用いられ始めており、これまで半導体業界に積極的に関わってこなかった企業にとっても大きなチャンスとなり得る。特に、精密研磨や精密制御等、条件出しや調整にノウハウや技術が必要な分野における新材料・装置が求められており、ここにノウハウを蓄えてきている日本企業に活躍のチャンスがあると考えられる。日本の装置・材料メーカーは、業界の垣根を越えて、これまで個社で培ってきた材料・装置における技術を、三次元実装技術に活用することを目指すべきである。

(※1) Tech Insights「EUV Lithography: A Power-Hungry Path to Innovation

」(参照2025年5月8日)

」(参照2025年5月8日)(※2) tom’s HARDWARE「Analyst firm raises alarm about EUV chipmaking tools — each consumes as much power as a small city, fabs to consume 54,000 Gigawatts by 2030

」(2024年10月)(参照2025年5月8日)

」(2024年10月)(参照2025年5月8日)(※3) TECH+「Intelが次世代パッケージとして採用を目指す「ガラスコア基板」の詳細を公開

」(2023年9月)(参照2025年4月17日)

」(2023年9月)(参照2025年4月17日)(※4) SAMSUNG「サムスン電子、業界初の5ナノベースの次世代ウェアラブルプロセッサを発売

」(2021年10月)(参照2025年5月8日)

」(2021年10月)(参照2025年5月8日)(※5) 大日本印刷「次世代半導体パッケージ向け“TGVガラスコア基板”を開発

」(2023年3月)(参照2025年5月8日)

」(2023年3月)(参照2025年5月8日)(※6) 日本電気硝子「CO₂レーザー加工対応ガラスコア基板の開発に着手

」(2024年12月)(参照2025年5月8日)

」(2024年12月)(参照2025年5月8日)(※7) ジャパンディスプレイ「世界最先端半導体次世代三次元集積技術を有するテック・エクステンションとの資本業務提携のお知らせ

」(2025年2月)(参照2025年5月8日)

」(2025年2月)(参照2025年5月8日)(※8) イノラックス

ウェブページ(参照2025年5月8日)

ウェブページ(参照2025年5月8日)(※9) キヤノン

ウェブページ(参照2025年5月8日)

ウェブページ(参照2025年5月8日)(※10) 東レエンジニアリング「半導体先端パッケージ向け大型ガラス基板検査装置の本格販売を開始~業界初の両面検査・内部欠陥検査を実現~

」(2025年2月18日)(参照2025年5月8日)

」(2025年2月18日)(参照2025年5月8日)(※11) AGC

ウェブページ(参照2025年5月8日)

ウェブページ(参照2025年5月8日)(※12) 日本電気硝子

ウェブページ(参照2025年5月8日)

ウェブページ(参照2025年5月8日)(※13) 日本電気硝子「CO₂レーザー加工対応ガラスコア基板の開発に着手

」(2024年12月)(参照2025年5月8日)

」(2024年12月)(参照2025年5月8日)(※14) 三菱マテリアル「半導体パッケージ向け「角型シリコン基板」を開発~世界最大級600mm角の四角形状シリコン基板~

」(2024年8月21日)(参照日2025年5月14日)

」(2024年8月21日)(参照日2025年5月14日)※記事は執筆者の個人的見解であり、日本総研の公式見解を示すものではありません。